一般来说,底板的千兆网大多选用RGMII和SGMII两种接口,也有可以拓展出更多网口的QSGMII接口。

这篇文章主要是对前两种常用的千兆网接口的介绍,以直观的方式对比这两种接口在引脚方面的不同,比较适合帮助初学者建立一个初步的印象,能够快速的了解RGMII和SGMII在接线方面区别。

下面先简单介绍一下RGMII这种接口:

RGMII均采用4位数据接口,工作时钟125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。

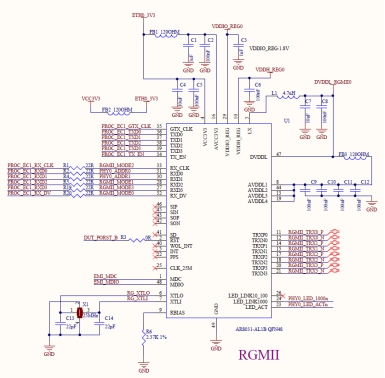

首先是硬件底板连接图。先是PHY芯片的AR8031的硬件接线图:

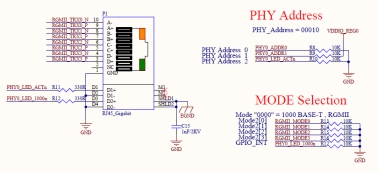

其次是网口座子和PHY芯片的模式选择引脚以及PHY地址的接线图:

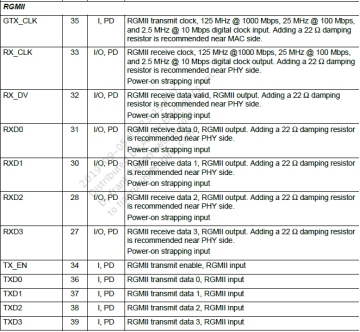

查阅AR8031的数据手册,先看硬件定义如下:

可见此接口引脚数量为12个。

其中发送端有:

n GTX_CLK:发送端参考时钟

n TXD[0:3]:发送数据引脚

n TX_EN:发送控制引脚

TX_EN信号线上传送TX_EN和TX_ER两种信息,在GTX_CLK的上升沿发送TX_EN,下降沿发送TX_ER。

注:在千兆速率下,向PHY提供GTX_CLK信号,TXD、TXEN、TXER信号与此时钟信号同步。否则,在10/100M速率下,PHY提供 TXCLK时钟信号,其它信号与此信号同步。其工作频率为25MHz(100M网络)或2.5MHz(10M网络)。

其中接收端有:

n RX_CLK:接收端参考时钟

n RXD[0:3]:接收数据引脚

n RX_DV:接收控制引脚

其余有一个管理配置接口,即MDIO接口,有2根线:

n MDC:时钟线

n MDIO:数据线(双向)

RGMII算是嵌入式开发板中非常常见的千兆以太网接口的接法了,但是随着近几年Serdes接口的大范围应用,SGMII这种使用两对差分线传输数据的千兆以太网接口出现的越来越普遍。相比较RGMII接口,SGMII接口使用的引脚数更少,相对应的时钟频率也更高。

下面简单的介绍一下这种接口:

SGMII即Serial GMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟信号的上升沿和下降沿均采样。

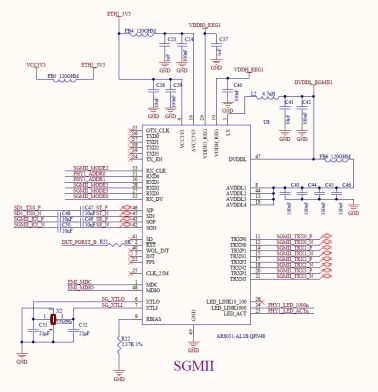

首先是硬件底板连接图。

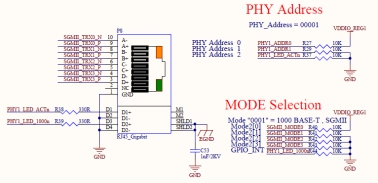

其次是网口座子和PHY芯片的模式选择引脚以及PHY地址的接线图:

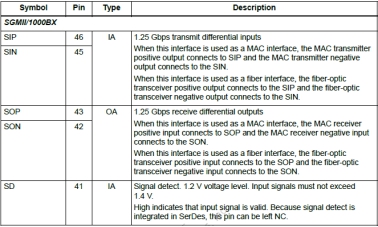

查阅AR8031的数据手册,先看硬件定义如下:

可见此接口引脚数量为4个,收发各一对差分信号线。

参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC侧没有时钟的情况,一般情况下,RX_CLK不使用,收发都可以从数据中恢复出时钟。

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。8B/10B变换的主要作用是扰码,让信号中不出现过长的连“0”和连“1”情况,影响时钟信息的提取。